ISSN: 1816-949X

© Medwell Journals, 2018

## A 31-Level Asymmetrical Cascaded H Bridge Multilevel Inverter

J. Gowrishankar and J. Belwinedward VIT University, Vellore, India

**Abstract:** This project commenced with a 31-level Asymmetrical Cascaded H-Bridge Multilevel Inverter (ASCHBMLI). The topology is based on a cascaded connection of single stage sub multilevel converter unit and full bridge cascaded H-bridge inverter. The input DC voltage source of  $V_{dc1}$ - $V_{dc4}$  are planned in paired type of voltage of 15  $V_{dc1}$ , 30  $V_{dc2}$ , 60  $V_{dc3}$  and 120  $V_{dc4}$  individually. The output voltage levels are 2\*(1+2+4+8)+1=31) 31 level. The low frequency pulse width modulation technique is utilized for controlling the power semiconductor switches in the ASCHBMLI. Total harmonic distortion is analyses and executed in real time system using PIC16F877A microcontroller.

**Key words:** The 31 level multilevel inverter, modulation technique and PIC16F877A controller, semiconductor, distortion, output, voltage

### INTRODUCTION

Inverter can be comprehensively characterized into single inverter and Multilevel Inverter (MLI). The Multilevel Inverter (MLI) solidify a power semiconductor switches (MOSFET, IGBT, etc., so on), DC voltage source and load (Alamria and Darwish, 2015).

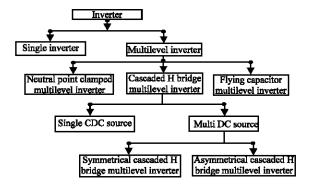

The output voltage of MLI which make the stepped waveforms over the load. In comparison with conventional two level Voltage Source Inverter (VSI), the multilevel inverter which pass on the "n" number of levels interminable supply of switches and DC source. It required for lessening the harmonic distortion and lower electromagnetic interference. On an incredibly essential level there are three sorts MLI, they are named Neutral point Clamped Multilevel Inverter (NPC-MLI), Cascaded H Bridge Multilevel Inverter (CHB-MLI) and Flying Capacitor Multilevel Inverter (FC-MLI) as showed up in Fig. 1.

Fig. 1: Classification of multilevel inverter

In MLI, the CHBMLI arrangement draws in more research consideration than FCMLI and NPCMLI because of their circuit simplicity and modularity. The CHB-MLI are named single DC source and multi DC source. In single DC source the CHB-MLI are assocaited in parallel. The ouput voltage of each H bridge, primary side of the transformer is associated where as the secondary side of transformers are related in sereis across the load. In multi DC source the CHB-MLI utilize the arrangement related to each cascaded H-Bridge cells with an isolates DC voltage sources associated with each cell (Paraniya and Sathick, 2016; Lee and Lee, 2013). The CHB multilevel inverters can be divided into two groups from the perspective of estimations of the DC voltage sources: the symmetric and the asymmetrical topology. In the symmetric topology, the DC voltage sources are indistinguishable. If the DC source to SCHBMLI are in the extent that is  $V_{\mbox{\tiny dc1}}\mbox{-}V_{\mbox{\tiny dc4}}\mbox{: is 1:1:1:1. So, the most exterem}$ ouput voltage is (2\*(1+1+1+1)+1 = 9) 9 level. In ASCHBMLI is to assemble the measure of output voltage level and the estimations of the DC voltage sources are chosen to parallel, these topologies are (Naresh et Asymmetrical topology 2014: Mokhberdoran and Ajami, 2014).

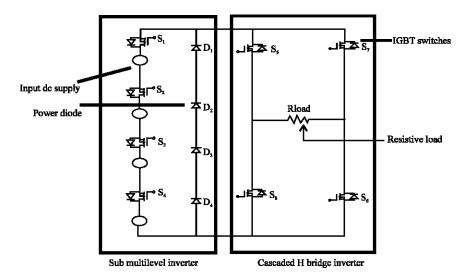

Asymmetrical multilevel inverter: Figure 2 demonstrates the each sub-multilevel inverters are associated in arrangement to accomplish the output voltage and number of levels. The sub-multilevel inverter comprises of DC voltage sources and IGBT switches. In IGBT a portion of the switches are unidirectional and others are bidirectional switches. The unidirectional switches control of Insulated Gate Bipolar Junction Transistor (IGBT) with

Fig. 2: The 31-level asymmetrical multilevel inverter

an anti-parallel diode. The DC voltage sources of Multilevel inverter are associated in arrangement to get the positive and zero to get the negative from the inverter in each half cycle the cascaded H bridge inverter associated in arrangement with sub multilevel inverters (Atithi and Patel, 2015; Prathiba and Renuga, 2012). The DC source of first, second, third and fourth sub multilevel inverter is  $V_{\text{dcl}}$ - $V_{\text{dcd}}$ :

$$V_{de2} = (n+1) * V_{de1}$$

(1)

$$V_{dc3} = (n+1) * V_{dc1} + V_{dc2}$$

(2)

$$V_{dc1} = (n+1)^{i-1} * V_{dc1}$$

$i = 1, 2, 3, ..., m$  (3)

The number of voltage levels will be equal to:

$$N_{level} = 2(n+1)^{m} - 1 (4)$$

N = Number of DC input sources

m = Number of sub multilevel in the system

$$N = 2 \text{ and } m = 4 \tag{5}$$

$$N_{level} = 2(4+1)^4 - 1 (6)$$

As per the asymmetrical topology, the estimation of the DC voltage sources is not the same as a submultilevel inverter to another. As such if the DC sources of the main submultilevel inverter is  $V_{\mbox{\tiny dcl}}$ , the DC source of the second submultilevel inverter is  $V_{\mbox{\tiny dcl}}$ . To get most extreme number

of level for the output voltage, there must be no repetition (Shankar and Edward, 2016). This is accomplished when the estimation of the DC voltage sources in submultilevel inverters have the accompanying connection. Note that the 31-level topology can be given through structure exhibited in Fig. 1 where the main distinction will be in the extremity of the connected DC voltage sources (Rawat and Chandel, 2013).

In ADCS the DC voltage source are in binary form of voltage like 15  $V_{\text{dc}},\,30$  V  $_{\text{dc}}$  60 V  $_{\text{dc}}$  and 120 V  $_{\text{dc}}$  So, the output voltage levels are 31 levels. The output voltage levels are 15  $V_{\text{dc}}$  30 V  $_{\text{dc}}$  45 V  $_{\text{dc}}$  60 V  $_{\text{dc}}$  75 V  $_{\text{dc}}$  90 V  $_{\text{dc}}$  105 V  $_{\text{dc}}$  120 V  $_{\text{dc}}$  135 V  $_{\text{dc}}$  150 V  $_{\text{dc}}$  165 V  $_{\text{dc}}$  180 V  $_{\text{dc}}$  195 V  $_{\text{dc}}$  210 V  $_{\text{dc}}$  225 V  $_{\text{dc}}$  0 V  $_{\text{dc}}$  -15 V  $_{\text{dc}}$  -30 V  $_{\text{dc}}$  -45 V  $_{\text{dc}}$  -60 V  $_{\text{dc}}$  -75 V  $_{\text{dc}}$  -90 V  $_{\text{dc}}$  -195 V  $_{\text{dc}}$  -120 V  $_{\text{dc}}$  -135 V  $_{\text{dc}}$  -150 V  $_{\text{dc}}$  -165 V  $_{\text{dc}}$  -180 V  $_{\text{dc}}$  -195 V  $_{\text{dc}}$  -210 V  $_{\text{dc}}$  -225 V  $_{\text{dc}}$ . The proposed sub-multilevel inverter can simply create zero and postitive voltage levels. The output voltage is gained when the switchs S1 and S1 are turned ON in the mean time. The other voltage levels are created by real trading between the switches. Suggests that the comparing switch is turned ON and 0 shows the OFF stat (Pols and Moring, 2012; Atallah *et al.*, 2014) (Table 1).

# Switching mode operation of 31-level asymmetrical MLI:

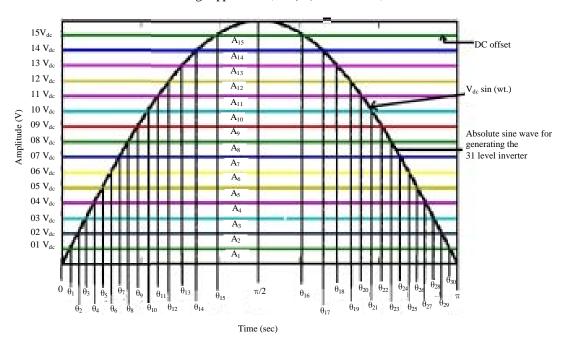

The switching technique of 31 level ASCHBMI as shown in Fig. 3 and 4. Conduction plots for switches are controlled by utilizing voltage reference technique. Voltage reference technique changes the switching angles into switching reference voltage. Figure 3 demonstrates the reference voltage waveform with each progression level. Switching reference voltage can be obtained as takes after (Fairchild Semiconductor, 2015). Conduction

Fig. 3: Reference voltage and step pulse area in 31-level inverter

| Factors                        | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $S_7$ | $S_8$ |

|--------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| $15  \mathrm{V}_{\mathrm{dc}}$ | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     |

| $14~\mathrm{V}_\mathrm{dc}$    | 0     | 1     | 1     | 1     | 1     | 1     | 0     | 0     |

| $13 V_{dc}$                    | 1     | 0     | 1     | 1     | 1     | 1     | 0     | 0     |

| $12\mathrm{V}_{\mathrm{dc}}$   | 0     | 0     | 0     | 1     | 1     | 1     | 0     | 0     |

| $11~ m V_{dc}$                 | 1     | 1     | 0     | 0     | 1     | 1     | 0     | 0     |

| $10 m V_{dc}$                  | 0     | 1     | 0     | 0     | 1     | 1     | 0     | 0     |

| $9 V_{dc}$                     | 1     | 0     | 1     | 0     | 1     | 1     | 0     | 0     |

| $8   m V_{dc}$                 | 0     | 0     | 1     | 0     | 1     | 1     | 0     | 0     |

| $7   m V_{dc}$                 | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     |

| 6 V <sub>dc</sub>              | 0     | 1     | 0     | 1     | 1     | 1     | 0     | 0     |

| 5 V <sub>dc</sub>              | 1     | 0     | 0     | 1     | 1     | 1     | 0     | 0     |

| $4 V_{dc}$                     | 0     | 0     | 0     | 1     | 1     | 1     | 0     | 0     |

| 3 V <sub>dc</sub>              | 1     | 1     | 1     | 0     | 1     | 1     | 0     | 0     |

| $2 V_{dc}$                     | 0     | 1     | 1     | 0     | 1     | 1     | 0     | 0     |

| $1 V_{dc}$                     | 1     | 0     | 1     | 0     | 1     | 1     | 0     | 0     |

| $0 V_{dc}$                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| $-1 V_{dc}$                    | 1     | 0     | 0     | 0     | 0     | 0     | 1     | 1     |

| $-2 V_{dc}$                    | 0     | 1     | 0     | 1     | 0     | 0     | 1     | 1     |

| $-3 V_{dc}$                    | 1     | 1     | 0     | 1     | 0     | 0     | 1     | 1     |

| $-4 V_{dc}$                    | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1     |

| -5 V <sub>dc</sub>             | 1     | 0     | 1     | 1     | 0     | 0     | 1     | 1     |

| -6 V <sub>dc</sub>             | 0     | 1     | 1     | 0     | 0     | 0     | 1     | 1     |

| -7 V <sub>dc</sub>             | 1     | 1     | 0     | 0     | 0     | 0     | 1     | 1     |

| -8 V <sub>dc</sub>             | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     |

| -9 V <sub>dc</sub>             | 1     | 0     | 0     | 0     | 0     | 0     | 1     | 1     |

| -10 $ m V_{dc}$                | 0     | 1     | 1     | 1     | 0     | 0     | 1     | 1     |

| $-11~ m V_{dc}$                | 1     | 1     | 1     | 1     | 0     | 0     | 1     | 1     |

| -12 $V_{dc}$                   | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1     |

| -13 $V_{ m dc}$                | 1     | 0     | 0     | 1     | 0     | 0     | 1     | 1     |

| $-14~{ m V}_{ m dc}$           | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 1     |

plots for switches are controlled by utilizing voltage reference strategy. Voltage reference strategy changes the changing points into exchanging reference

-15 V<sub>d</sub>

voltage. Figure 3 demonstrates the reference voltage waveform with each progression level. Exchanging reference voltage can be gotten as takes after:

$$V_{ref} = m*V_{dc}*M_{i}*sin(wt)$$

(7)

Where:

m = No. of voltage levels of cascade inverter during one cycle

$M_i = Modulation index = V^*/V_{max}$

V\* = Amplitude of reference Voltage

$V_{max}$  = Maximum amplitude of cascade inverter

m = 15 and  $M_{\rm I}$ =1, then  $V_{\rm ref}$ =15\* $V_{\rm dc}$ \*sin(wt)

Here, reference waveform is isolated into number of ranges which is equivalent to number of ventures in one cycle and the voltage second zone of reference voltage waveform is equivalent to output voltage waveform of inverter. In every range convergence point known as sham edges can be computed by using  $\theta_k{}^1 = \sin^{-1}\left(k/m\right)$  where  $K=1,\,2,\,3$  (M-1). Then area  $A_1,\,A_2,\,\ldots,\,A_J$  can be obtained by using dummy switching angle:

$$A_{1} = \int_{0}^{\theta_{1}^{1}} 15 V_{dc} \sin(wt) d(wt) + \int_{\theta_{1}^{1}}^{\pi/2} V_{dcd}(wt)$$

(8)

$$A_{2} = \int_{0}^{\theta_{2}^{l}} 15V_{dc} \sin(wt)d(wt) + \int_{\theta_{21}}^{\pi/2} V_{dcd}(wt) - A_{1}$$

(9)

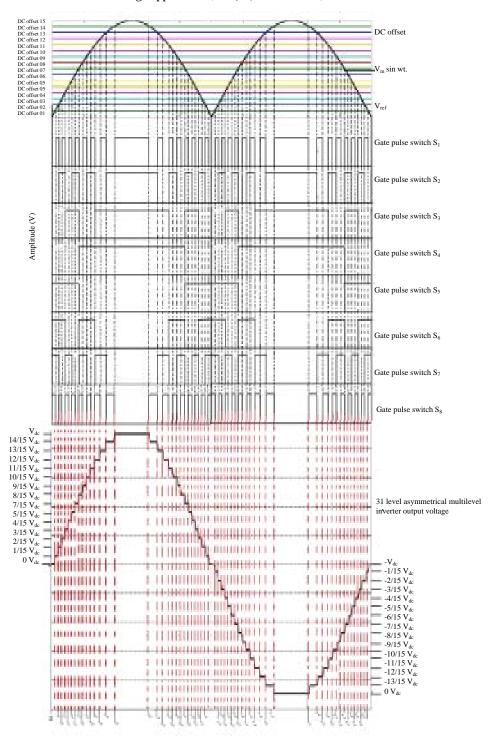

Fig. 4: Switching combination of 31-level inverter

$$A_{j} = \int\limits_{0}^{\theta_{j}^{l}} m V_{\text{dc}} \sin(wt) d(wt) + \int\limits_{\theta_{j1}^{l}}^{\pi/2} j V_{\text{dcd}}(wt) - \sum\nolimits_{i=1}^{j-1} A_{j} \eqno(10)$$

Figure 4 shows the switching combination of asymmetrical cascaded H bridge multilevel inverter. In this

circuit the low frequency pulse width modulation is used for controlling the switches in 31-level asymmetrical inverter. The DC offset is compared with the absolute sine wave. Depending upon the logical circuit like AND, OR, NOT, etc., the switching technique is used for generating the gate pulse. In the system, the output level is positive

15 level, negative 15 level and zero level one. According to this the 15 DC offset are generated and compared with absolute sine wave to produce the switching pulse from switch S<sub>1</sub>-S<sub>8</sub>.

In next step shows the output voltage level of 31 level asymmetrical inverter. The output voltage level are 15  $V_{\rm dc}$  14  $V_{\rm dc}$ 13  $V_{\rm dc}$  12  $V_{\rm dc}$  11  $V_{\rm dc}$  10  $V_{\rm dc}$  09  $V_{\rm dc}$  08  $V_{\rm dc}$  07  $V_{\rm dc}$  06  $V_{\rm dc}$  05  $V_{\rm dc}$  04  $V_{\rm dc}$  03  $V_{\rm dc}$  02  $V_{\rm dc}$  01  $V_{\rm dc}$  00  $V_{\rm dc}$  -01  $V_{\rm dc}$  -02  $V_{\rm dc}$  -03  $V_{\rm dc}$  -04  $V_{\rm dc}$  -05  $V_{\rm dc}$  -06  $V_{\rm dc}$  -07  $V_{\rm dc}$  -08  $V_{\rm dc}$  -09  $V_{\rm dc}$  -10  $V_{\rm dc}$  -11  $V_{\rm dc}$  -12  $V_{\rm dc}$  -13  $V_{\rm dc}$  -14  $V_{\rm dc}$  and -15  $V_{\rm dc}$

### RESULTS AND DISCUSSION

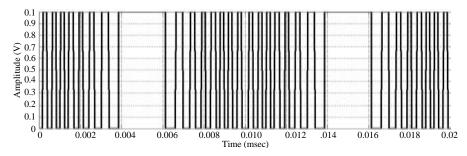

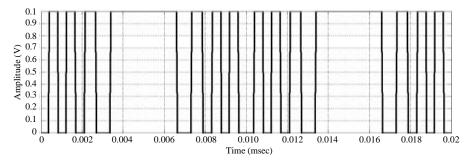

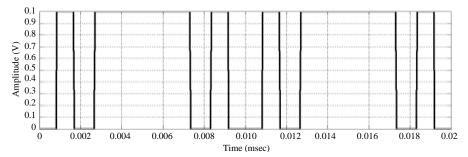

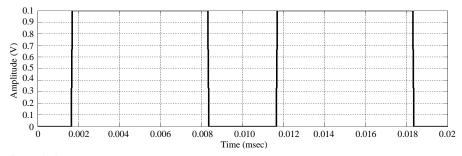

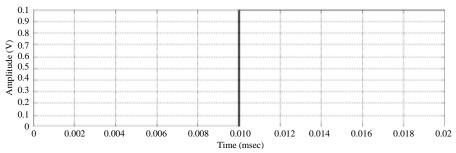

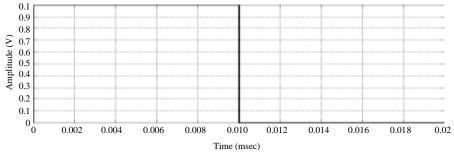

Figure 5-10 shows the switching gate pulse for 31-level asymmetrical cascaded multilevel inverter. This switching technique are design by using DC offset of low frequency pulse width modulation. To reduce the

switching losses in the system the low frequency pulse width modulation has implemented in this switching technique.

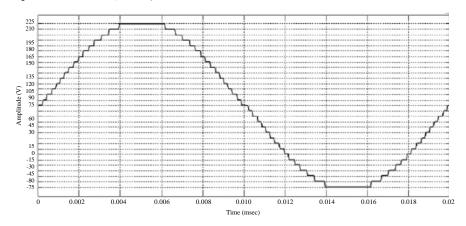

The output voltage of 31-level inverter as shown in Fig. 11. The output voltage levels are 15  $V_{do}$  30  $V_{do}$  45  $V_{do}$ , 60  $V_{do}$  75  $V_{do}$  90  $V_{do}$  105  $V_{do}$  120  $V_{do}$  135  $V_{do}$  150  $V_{do}$  165  $V_{do}$  180  $V_{do}$  195  $V_{do}$  210  $V_{do}$  225  $V_{do}$ 0  $V_{do}$ -15  $V_{do}$ -30  $V_{do}$ -45  $V_{do}$ -60  $V_{do}$ -75  $V_{do}$ -90  $V_{do}$ -105  $V_{do}$ -120  $V_{do}$ -135  $V_{do}$ -150  $V_{do}$ -165  $V_{do}$ -165  $V_{do}$ -180  $V_{do}$ -195  $V_{do}$ -210  $V_{do}$ -225  $V_{do}$  respectively. The total harmonics distortion for 31-level inverter is 3.25% (Jayapalan and Edward, 2017).

**Hardware:** The real time implementation of 31-level inverter using PIC16F877A microcontroller with RL load as shown in Fig. 12. In this system, the PIC16F877A Microcontroller are used for generating gate pulse to control the MOSFET switch in the inverter. The MOSFET Driver circuit is used to step up the gate voltage

Fig. 5: Gate pulse for switch S<sub>1</sub>

Fig. 6: Gate pulse for switch S<sub>2</sub>

Fig. 7: Gate pulse for switch S<sub>3</sub>

## J. Eng. Applied Sci., 13 (12): 4542-4550, 2018

Fig. 8: Gate pulse for switch S<sub>4</sub>

Fig. 9: Gate pulse for switch  $S_5$  and  $S_6$

Fig. 10: Gate pulse for switch S<sub>7</sub> and S<sub>8</sub>

Fig. 11: Output voltage of 31-level asymmetrical MLI

form 5-12 V. The IRF640 Mosfet switch is used in the inverter circuit. The input DC voltage are 3  $V_{\text{do}}$  6  $V_{\text{do}}$  12  $V_{\text{dc}}$  and 24  $V_{\text{dc}}$  (Shankar and Edward, 2016a, b).

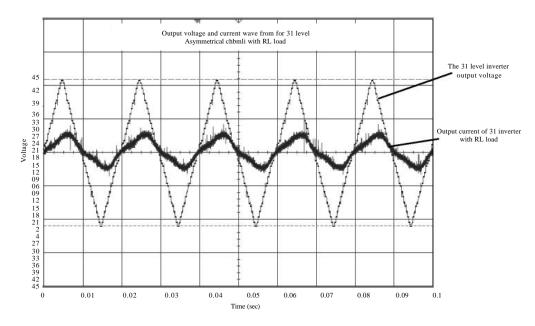

The output voltage and current waveform as shown in Fig. 13. The 31 level inverter using RL load which consists of resistance 100  $\Omega$  and inductance 5 mH. The output voltage for the inverter is 45  $V_{\text{dc}}$  42  $V_{\text{dc}}$  39  $V_{\text{dc}}$

$\begin{array}{l} 36\,V_{\text{dc}},\,33\,V_{\text{dc}},\,30\,V_{\text{dc}},\,27\,V_{\text{dc}},\,24\,V_{\text{dc}},\,21\,V_{\text{dc}},\,18\,V_{\text{dc}},\,15\,V_{\text{dc}},\,12\\ V_{\text{dc}},\,9\,V_{\text{dc}},\,6\,V_{\text{dc}},\,3\,V_{\text{dc}},\,0\,V_{\text{dc}},\,-3\,V_{\text{dc}},-6\,V_{\text{dc}},-9\,V_{\text{dc}},-12\,V_{\text{dc}},-15\\ V_{\text{dc}},\,-18\,V_{\text{dc}},\,-21V_{\text{dc}},\,-24\,V_{\text{dc}},-27\,V_{\text{dc}},-30\,V_{\text{dc}},\,-33\,V_{\text{dc}},\,-36\,V_{\text{dc}}\\ \end{array}$

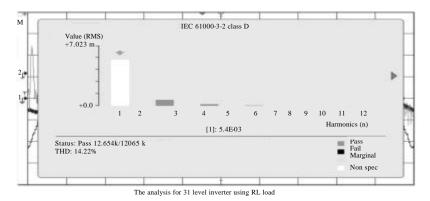

-39  $V_{do}$  -42  $V_{do}$ . The THD analysis for 31-level inverter as shown in Fig. 14. The THD is analyzed for 31 level inverter using RL load is 14.22%. In this system the first order

Fig. 12: Hardware implementation of 31-level inverter using RL load

Fig. 13: Output voltage and current waveform for 31-level inverter using RL load

Fig. 14: THD analysis for 31-level inverter

Fig. 15: Output voltage and current waveform for 15-level inverter using RL load

Fig. 16: THD analysis for 15-level inverter

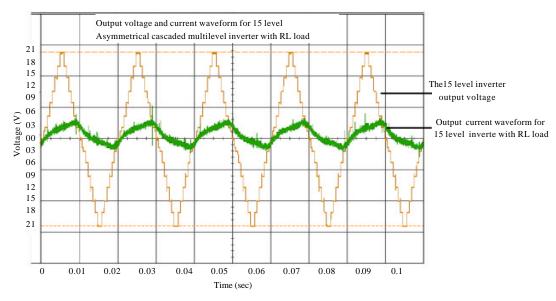

harmonics is very high when compared with other harmonics. The output voltage and current waveform as shown in Fig. 15. The input DC voltage source for 15-level inverter is 3  $V_{\rm de}$  6  $V_{\rm dc}$  and 12  $V_{\rm dc}$ . The 15 level inverter with RL load which consists of resistance 100  $\Omega$  and inductance 5 mH. The output voltage for the inverter is 21  $V_{\rm de}$  18  $V_{\rm de}$  15  $V_{\rm de}$  12  $V_{\rm de}$  9  $V_{\rm de}$  6  $V_{\rm de}$  3  $V_{\rm de}$  0  $V_{\rm de}$  -3  $V_{\rm de}$  -6  $V_{\rm de}$  -9  $V_{\rm de}$  -12  $V_{\rm de}$  -15  $V_{\rm de}$  -18  $V_{\rm de}$  and -21  $V_{\rm de}$

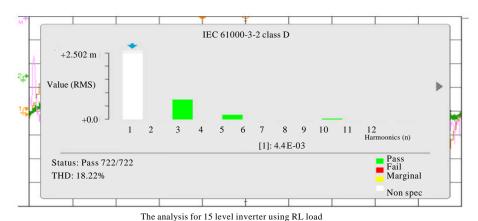

The THD analysis for 15 level inverter as shown in Fig. 16. The THD is analyzed for 31 level inverter using RL load is 18.22%. In this system, the first order harmonics and third order harmonics is very high when compared with other harmonics. While comparing the 15 and 31-level the third order harmonics is very high in 15 level.

### CONCLUSION

The 15 and 31-level asymmetrical cascaded H bridge multilevel inverter are analyzed in this system. The low frequency pulse width modulation techniques is used for generating the gate pulse for inverter. In three DC voltage source are  $V_{\text{dc1}} = 3 \text{ V}$ ,  $V_{\text{dc2}} = 6 \text{ V}$ ,  $V_{\text{dc3}} = 12 \text{ V}$  used along with RL load to generate the 15 level inverter and THD is analyzed for 15 level inverter is 18.22% where as in the four DC voltage source are  $V_{\text{dc1}} = 3V$ ,  $V_{\text{dc2}} = 6 \text{ V}$ ,  $V_{\text{dc3}} = 12 \text{ V}$  and  $V_{\text{dc}} = 24 \text{ V}$  used along with RL load to generate the 31 level inverter and the THD is analyzed for 31-level inverter is 14.22%. So the THD is reduce my increasing the levels. The THD for 31-level inverter is 14.22%. As per the THD analysis 31-level inverter is better performance of system.

### REFERENCES

- Alamria, B. and M. Darwish, 2015. Power loss investi gation for 13 level cascaded h bridge multilevel inverter. J. Energy Power Sour., 2: 230-238.

- Atallah, A.M., A.Y. Abdelaziz and R.S. Jumaah, 2014. Implementation of perturb and observe MPPT of PV system with direct control method using buck and buck-boost converters. Emerging Trends Electr. Electron. Instrum. Eng. Intl. J., 1: 31-44.

- Atithi, B.P. and H.H. Patel, 2015. Control of asymmetric cascaded H-bridge multilevel inverter. Intl. J. Current Eng. Sci. Res., 2: 44-49.

- Fairchild Semiconductor, 2015. PWM switch modeling in flyback converter using 2nd stage LC filter. Fairchild Semiconductor, Sunnyvale, California, USA. https://www.digikey.com/en/articles/techzone/2015/apr/pwm-switch-modeling-in-flyback-converter-using-2nd-stage-lc-filter

- Jayapalan, G. and B. Edward, 2017. Design and implementation of 15-level asymmetrical cascaded H bridge multilevel inverter. J. Electr. Eng., 2017: 1-9.

- Lee, J.S. and K.B. Lee, 2013. Variable dc-link voltage algorithm with a wide range of maximum power point tracking for a two-string PV system. Energ., 6: 58-78.

- Mokhberdoran, A. and A. Ajami, 2014. Symmetric and asymmetric design and implementation of new cascaded multilevel inverter topology. IEEE. Trans. Power Electron., 29: 6712-6724.

- Naresh, K.M., M. Umavathi and H.R. Mohan, 2014. Multi output fly back converter with switching-linear post regulators. Intl. J. Recent Dev. Eng. Technol., 2: 21-26.

- Paraniya, P. and M.J. Sathick, 2016. A new multilevel inverter with reduced maximum blocking voltage. Proceedings of the 2016 International Conference on Current Research in Engineering Science and Technology (ICCREST'16), April 05, 2016, Jayaram College of Engineering and Technology-JCET, Pagalavadi, India, pp. 26-34.

- Pols, A. and S. Moring, 2012. Maximum power point tracking: Algorithm and software development. Master Thesis, Delft University of Technology, Delft, Netherlands.

- Prathiba, T. and P. Renuga, 2012. A comparative study of Total Harmonic Distortion in Multi level inverter topologies. J. Inf. Eng. Appli., 2: 26-36.

- Rawat, R. and S. Chandel, 2013. Hill climbing techniques for tracking maximum power point in solar photovoltaic systems-a review. Intl. J. Sustain. Dev. Green Econ., 2: 90-95.

- Shankar, G.J. and B. Edward, 2016b. Implementation of 5-level cascaded H-bridge multilevel inverter with single DC source for photo voltaic system using proteus. J. Electr. Eng., 16: 127-132.

- Shankar, J.G. and J.B. Edward, 2016a. A 15-level asymmetric cascaded H bridge multilevel inverter with less number of switches for photo voltaic system. Proceedings of the 2016 International Conference on Circuit Power and Computing Technologies (ICCPCT'16), March 18-19, 2016, IEEE, Nagercoil, India, ISBN:978-1-5090-1278-7, pp: 1-10.