ISSN: 1816-949X

© Medwell Journals, 2016

# A Piezoelectric Energy Harvesting Interface Circuit Using Negative Voltage Converter

Allenn C. Lowaton and Qadier I. Jilluh

Microelectronics Lab/Complex Systems Initiative,

Department of Electrical/Electronics/Computer Engineering,

Mindanao State University, Iligan Institute of Technology, Iligan City, Philippines

Abstract: This study presents a piezoelectric energy harvesting system electric interface which includes two main sections; a rectifier and a voltage regulator. The negative voltage converter, an improved version of the full bridge rectifier coupled with an active diode implementation is used to convert the extracted AC power from the transducer. The simulation results shows that the power extraction efficiency of the proposed rectifier is 2.2 times that of a conventional full bridge rectifier and >82% of power conversion can be achieve. To complete the harvesting system a low powered DC-DC Buck converter is used to regulate the power extracted by the rectifier to run a wireless sensor node operating at 1.5 V voltage and 2 mA current. The buck converter has a load regulation measured at 0.18 mV/mA and a line regulation of 0.18 mV/V. The buck converter has a maximum efficiency of 84% with 1% voltage ripple. The die size for the overall layout is 1008×1008 µm including pad.

Key words: Energy harvesting, negative voltage converter, piezoelectric, efficiency, negative voltage

## INTRODUCTION

With the advancement of the electronic devices that are mobile, portable with less weight, there is also a need for power generation with high efficiency. Conventionally, for such applications having constraints on size, less weight, safety concerns and longevity, the battery handles most of them. Apparently, for some applications, a new source of energy must be utilized apart aside from battery. Such applications are wireless sensor networks, implantable devices, tire pressure sensor systems and others. A new source of energy that is flexible and widely available is highly needed.

Recently, a number of researches have been done on vibration energy harvesters. Their application ranges from wearable electronic devices, implantable devices and wireless sensor nodes (Dallago et al., 2008; Do et al., 2011; Kymissis et al., 1998; Lesieutre et al., 2004; Liou et al., 2008). The main challenge of harvesting energy from vibrations is its relatively low output AC voltage. This distinct characteristic is indeed a challenge especially when working on most rectifier circuits that utilized diodes in their circuitry. That rectifier requires a nonzero turn-on voltage in its operation.

## Literature review

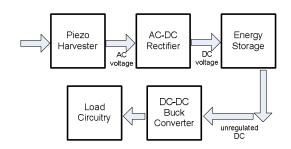

Theoretical framework: This section describes the theoretical framework for the piezoelectric energy harvesting system. The main blocks of the system are shown in Fig. 1 which includes a rectifier circuit, energy storage and the DC-DC buck converter which will then on deliver power to the load application. The DC-DC buck converter is divided further into several functional blocks: error amplifier circuit, biasing circuit, Vref circuit which is independent of the supply, hysteresis comparator, ramp generator, non-overlapping buffer and the PWM which activates during heavy loads the feedback and compensation.

Fig. 1: Piezoelectric energy harvesting system

Corresponding Author: Allenn C. Lowaton, Microelectronics Lab/Complex Systems Initiative,

Department of Electrical/Electronics/Computer Engineering, Mindanao State University,

Iligan Institute of Technology, Iligan City, Philippines

The input of the system is in the form of a vibration which will be converted into usable AC voltage by the piezoelectric transducer. AC voltage is then rectified and inputted to a regulator to power up the chosen load application for the harvesting system (Ottman *et al.*, 2007).

#### MATERIALS AND METHODS

This study discusses actual process in which the design proper of the project is carried on. The succeeding section will discuss the design flow, as well as the block design integration of the entire system. Finally, the design specification is declared and the schematic of every part of the entire block is discussed.

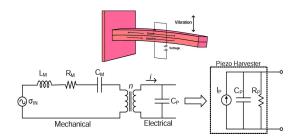

**Piezoelectric transducer equivalent circuit Figure:** Shown in the Fig. 2 is the equivalent circuit diagram of the piezoelectric energy harvester. An input vibration being applied to the material will cause a mechanical strain that will convert it to an electrical charge. Lead Zirconate Titanate (PZT) is a very common for this type of power generation. Note that the output electrical voltage is AC.

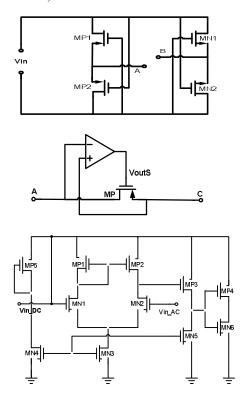

AC-DC rectifier: The piezoelectric energy harvester collects some waste energy from vibrations from rotating machines then converts it into an electrical energy. An AC voltage can be obtained from the extracted piezoelectric strain energy. However, that output is very low in magnitude. On top of that, low power electronic devices nowadays require a low DC voltage in its operation. With this, there is a need to rectify and convert the AC into a usable DC. Shown in Fig. 3a is a negative voltage converter. This circuit converts the negative cycle of the input sinusoidal wave into positive. The said conversion is being done only by using four MOS transistors. The NMOS at the right part of the circuit ensures that the lowest potential of Vin should be delivered to point B. On the other hand, the PMOS on the left side make sure that the highest potential will always be delivered at point A. With this, the bulk of the PMOS can be directly connected to point A while that of the NMOS can be connected directly to point B. Thus, it reduces the required number of transistors for this implementation.

This circuit has the ability to convert the entire input voltage. It has a very low voltage drop of below 10 mV (Peters *et al.*, 2007). However, this circuit has a problem; it cannot be used to charge a storage capacitor since its current direction is not controlled and current back flow might occurs. Shown in Fig. 3b is the active diode implementation. The function of this circuit is to current direction control. It can be implemented using a simple diode connected MOS. Also shown in Fig. 2 and 3

Fig. 2: Equivalent circuit diagrams of a piezoelectric energy harvester (Ramadass and Chandrakasan, 2010)

Fig. 3: a) Negative voltage converter; b) Active diode implementation; c) Comparator architecture

is a comparator. It must be fast with low power consumption. The design of the comparator is vital for the operation. If the comparator is too slow not all available energy can be transferred to the capacitor and additionally current back flow occurs after the input voltage has passed the maximum value, also if the comparator is made too fast it will essentially draw too much power consumption and eventually lessen the efficiency of the circuit.

Figure 3 shows the comparator circuit. It has a differential stage, a common source output amplifier and an inverter. The input Vin, DC is connected to the cathode

Figure 3b and is also the power supply of the comparator. While V in, AC is connected to the alternating sinusoidal input wave (anode a) or the output one of the output of the negative voltage converter shown in Fig. 3a.

**Energy storage:** Batteries can be replaced by utilizing the super-capacitors. It has the advantages of having more charge and discharge cycles. Aside from that, it also has high power density, very efficient, lasts longer and less toxic compared to batteries.

For this particular system, the chosen energy storage is the Maxwell PC 10 Super capacitor. The maximum energy of this storage is only at 6.9 mAh. If compared to other energy storage, it can be noted that it is typically low but the chosen load application would only require 3mAh of energy to operate and it won't be operating continuously for a long period of time. One of the major advantage of a super capacitor is shown above, its lifespan and number to charge cycles.

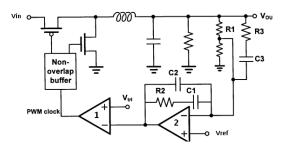

**DC-DC regulator specifications:** In this research, DC-DC step-down (buck-type) switching mode converter shown in Fig. 4 was designed by utilizing the advantages of Pulse Width Modulation. The general specifications of the power converter are stated in Table 1. This designed converter utilizes the 0.18 um CMOS Process which was the acquired licensed of MSU-IIT from Synopsys. And the rest of the desired specifications were taken from stated references of this paper, so that, the designer could compare the result easily.

Load applications: The piezoelectric energy harvester being considered for this particular paper operates around 80-240 Hz. This type of mechanical vibration can be harvested from industrial establishments which uses big machineries. Thus, the end circuit application of the harvested energy from the entire system could range from condition monitoring sensors to wireless sensor networks which uses power in the range of uW.

The target application of this design is the Microsemi's ZL70250. It is a wireless sensor network transceivers optimized for low-power consumption and it works with energy harvesting sources. The Microsemi's ZL 70250 dissipates <2 mA at a supply voltage of 1.2-1.8 V. Thus, this helps determine the output specification of the voltage regulator design for this research (Ramadass and Chandrakasan, 2010; Resali and Salleh, 2010; Sun *et al.*, 2012).

#### RESULTS AND DISCUSSION

This study discusses the result of the simulation of the presented circuit architecture from the methodology

Fig. 4: PWM buck converter

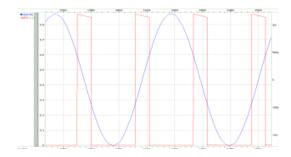

Fig. 5: Output signal from low power comparator used in the rectifier circuit

study. The results are tabulated and then discussed accordingly.

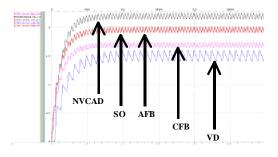

Negative voltage converter with active diode: Figure 5 shows the signal which controls the active diode in the rectifier circuit. Figure 6 presents the output of 4 different rectifier architecture designs and being compared with the results to proposed Negative voltage converter with Active Diode Rectifier output. As what was discussed from the previous chapter, the main purpose of the active diode implementation is to control the direction of the current output of the rectifier. As what is seen in the figure, the comparator turns on every time the input current changes polarity and thus making sure that the current output is always positive.

Table 2 depicts the summary of the results of the simulation of the rectifier circuits shown in Fig. 3. All the rectifiers are simulated with the following transducer parameters:  $I_p$  = 900uA,  $f_p$  = 200Hz,  $C_p$  = 18nF and  $R_p$  = 1k $\Omega$  As what is seen both in Fig. 6 and Table 2, the proposed rectifier architecture can harvest greater energy compared to the other architecture given the same sizes of MOS and the same input and output parameters.

**PWM buck converter:** This study will discuss the output of PWM buck converter, graphs will be shown and

Table 2: Summary of results for rectifier

| Architecture            | Average Vout | Average Pout (mW | Power compared to conventional FB (%) | Efficiency (PDC/PAC) (%) |

|-------------------------|--------------|------------------|---------------------------------------|--------------------------|

| Conventional FB         | 1.50103      | 0.901            |                                       | 54.0                     |

| Voltage doubler         | 1.69322      | 1.147            | 127                                   | 52.0                     |

| Cross-coupled rectifier | 1.96843      | 1.52             | 169                                   | 64.2                     |

| Switch only             | 1.95029      | 1.549            | 172                                   | 65.0                     |

| NVCAD (pre-simulation)  | 2.23885      | 2.0054           | 222.5                                 | 85.2                     |

| NVCAD (post-simulation) | 2.22858      | 1.9866           | 220.5                                 | 82.1                     |

Summary of results @ W = 20 um L = 1 um M = 20 @ Load; Cap = 18 uF, Res =  $2.5 \text{ K}\Omega$

Table 3: Buck converter specifications

| Variables                  | Pre-simulation                              | Post-simulation                               |

|----------------------------|---------------------------------------------|-----------------------------------------------|

| Input voltage              | 1.5-2.5 V                                   | 1.5-2.5 V                                     |

| Output voltage             | 1.5 V                                       | 1.5 V                                         |

| Switching frequency        | 400 kHz                                     | 400 kHz                                       |

| Output current             | 1.5-2 mA                                    | 1.5-2 mA                                      |

| Load resistance            | 750-1000 Ω                                  | $750-1000\Omega$                              |

| Inductor (off-chip)        | 15 uH                                       | 15 uH                                         |

| Capacitor (off-chip)       | 3 uH                                        | 3 uH                                          |

| RC compensation (off-chip) | 12 pF 0.4 pF 12 pF 1.1 MΩ 1.85 MΩ 1 KΩ      | 12 pF 0.4 pF 12 pF 1.1 MΩ 1.85 MΩ 1 KΩ        |

| Output ripple voltage      | 0.78% at 2.5 V input                        | 0.925% at 2.5 V input                         |

| Phase margin               | 54°                                         | 53.6°                                         |

| Load regulation            | $0.06  \text{mVmA}^{-1}$                    | $0.18  \mathrm{mV  mA^{-1}}$                  |

| Line regulation            | $0.1  \mathrm{mV}  \mathrm{V}^{-1}$         | 0.18 mV/V                                     |

| Efficiency                 | 84.5% at 2.5V input and 2 mA output current | 83.92% at 2.5 V input and 2 mA output current |

| Chip area                  |                                             | 508×210 um                                    |

Fig. 6: Overlay of outputs of 5 different rectifier architecture (NVCAD) Negative Voltage Converter with Active Diode and 4 other architectures namely; (SO) Switch Only (AFB) Active Full-Bridge (CFB) Conventional Full-Bridge and (VD) Voltage Doubler

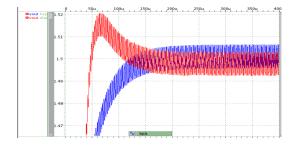

Fig. 7: Pre and post-simulation of buck converter

buck converter for its post and pre-simulation result. As the specification will be discussed in a Table 3 shown in Fig. 7 is the overlay of the output of the designed PWM

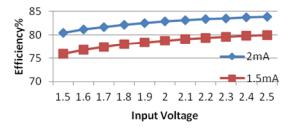

Fig. 8: Buck converter efficiency plot chart

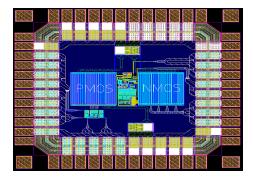

Fig. 9: Chip layout implementation

what is shown, the output voltage is still constant at 1.5 V event after extraction of parasitic in the layout is done. Figure 8 shows the plot of the efficiency of the converter over a wide range of current and voltage, it can however be noted that the highest efficiency is recorded at 2.5 V and 2 mA which is as expected. The summary of the converter performance is shown in Table 3. The tabulated

Table 4: Comparison with the other works

| rable 1. Comparis     | on man are outer         | ** OI IXS           |                      |

|-----------------------|--------------------------|---------------------|----------------------|

| SPECS                 | Sun <i>et al.</i> (2012) | Do et al. (2011)    | This work            |

| Technology            | 0.18 μm                  | 0.18 μm             | 0.18 μm              |

| Vin, peak (V)         | 3                        | 1.9                 | 2.38                 |

| Vrect (V)             | 2.78                     | 1.87                | 2.37                 |

| Fc (Hz)               | 200                      | 200                 | 120                  |

| Rectifier architectu  | re Resetting             | Synchronized switch | NVCAD                |

| Rectifier inductor    | No                       | No                  | NO                   |

| External supply       | Yes                      | Yes                 | NO                   |

| P <sub>out</sub> (uW) | 81                       | 166                 | 234                  |

| Area (mm2)            | $0.25 \times 0.61$       | $0.20 \times 0.36$  | 86.5×49.5 μm         |

| Rectifier efficiency  | N/A                      | N/A                 | 82.1%                |

| Compared with CF      | B X 1.9                  | X 1.95              | X 2.2                |

| DC-DC used            | None                     | LDO                 | Buck                 |

| Load regulation       | None                     | 3.5V/A              | $0.18\mathrm{mV/mA}$ |

| Line regulation       | None                     | N/A                 | $0.18 \mathrm{mV/V}$ |

| Input voltage         | None                     | N/A                 | 1.5-2.5 V            |

| Output voltage        | None                     | 1.3V                | 1.5 V                |

| Output current        | N/A                      | 5 uA-10mA           | 1.5-2 mA             |

| DC-DC efficiency      | N/A                      | 90% (max)           | 84% (typ)            |

| k                     | N/A                      | N/A                 | 68.98 %              |

| Chin area             | N/A                      | N/A                 | 508×210 um           |

efficiency, line regulation, load regulation and ripple presented were taken from the optimum performance and at the nominal input voltage of the converter. The desired specification is achieved. Figure 9 is the chip layout implementation of this work. It has an area of 508×210 µm.

Simulation summary and comparison with the other works: Table 4 shows the comparison results of this work with other piezoelectric energy harvesting systems. The designed energy harvesting system is superior compared to other works in terms of circuit simplicity and efficiency. Advantage of this work compared to previous works on pieozoelectric energy harvesting system is its higher conversion efficiency without employing an inductor and a negative supply voltage in the rectifier stage of the system. Compared to 2 other works presented in Table 4, this research exhibits higher power extraction compared to conventional full bridge, while maintaining a relatively low area of the rectifier.

## CONCLUSION

The negative voltage converter with active diode architecture has been proposed. It has been shown that it can extract equal or superior output power while maintaining circuit simplicity compared to other existing works. The project was considered successful since the proposed design achieved and met the specified requirements to be able to run the load application chosen. This is specifically proposed to obtain an appreciable efficiency so as not to waste the scavenge energy. Additionally, smaller overall layout area was achieved. The efficiency of the converter is measured at 84%, even though, there is no rule of thumb but every design aims the highest outcome so a probable improvement is mentioned below.

The proponents of this thesis recommend the following for the improvement for future studies in this field: The use of an on-chip super-capacitor which will serve as the energy storage will make the system more compact and smaller in size. Further improvement of this study can be done by applying more tests to each of the blocks involved. Upon integration of the entire system in post-simulation, an unnatural oscillation caused by the post parasitic of the BJT model of the bandgap reference circuit is observed. Therefore, the proponent of this thesis recommends further test on the bandgap circuit, most especially on the BJT model.

## **ACKNOWLEDGEMENTS**

We are grateful for the Engineering Research and Development for Technology (ERDT) scholarship for Researchers would like to express gratitude to North Central Mindanao College, Maranding, Lala, Lanao del Norte, Philippines for the international travel funds being provided.

### REFERENCES

Dallago, E., D. Miatton, G. Venchi, V. Bottarel, G. Frattini, G. Ricotti and M. Schipani, 2008. Active autonomous AC-DC converter for piezoelectric energy scavenging systems. Proceedings of the IEEE Custom Integrated Circuits Conference, September 21-24, 2008, San Jose, CA., USA., pp: 555-558.

Do, X.D., C.J. Jeong, H.H. Nguyen, S.K. Han and S.G. Lee, 2011. A high efficiency piezoelectric energy harvesting system. Proceedings of the 2011 International Conference on SoC Design Conference (ISOCC), November 17-18, 2011, IEEE, Deajeon, South Korea, ISBN:978-1-4577-0709-4, pp: 389-392.

Kymissis, J., C. Kendall, J. Paradiso and N. Gershenfeld, 1998. Parasitic power harvesting in shoes. Proceedings of the 2nd International Symposium On Wearable Computers, October 19-20, 1998, Pittsburgh, PA, pp. 132-139.

Lesieutre, G.A., G.K. Ottman and H.F. Hofmann, 2004. Damping as a result of piezoelectric energy harvesting. J. Sound Vibration, 269: 991-1001.

Liou, W.R., M.L. Yeh and Y.L. Kuo, 2008. A high efficiency dual-mode buck converter IC for portable applications. IEEE. Trans. Power Electr., 23: 667-677.

Ottman, G.K., H.F. Hofmann, A.C. Bhatt and G.A. Lesieutre, 2007. Adaptive piezoelectric energy harvesting circuit for wireless remote power supply. IEEE Trans. Power Electron., 17: 669-676.

- Peters, C., O. Kessling, F. Henrici, M. Ortmanns and Y. Manoli, 2007. CMOS integrated highly efficient full wave rectifier. Proceedings of the 2007 IEEE International Symposium on Circuits and Systems, May 27-30, 2007, IEEE, Freiburg im Breisgau, Germany, ISBN:1-4244-0920-9, pp. 2415-2418.

- Ramadass, Y.K. and A.P. Chandrakasan, 2010. An efficient piezoelectric energy harvesting interface circuit using a bias-flip rectifier and shared inductor. IEEE J. Solid-State Circ., 45: 189-204.

- Resali, M.S.M. and H. Salleh, 2010. Comparison of energy harvesting power management techniques and application. Proceedings of the 34th IEEE/CPMT International Electronic Manufacturing Technology Symposium, November 30-December 2, 2010, Melaka, Malaysia, pp: 1-5.

- Sun, Y., N.H. Hieu, C.J. Jeong and S.G. Lee, 2012. An integrated high-performance active rectifier for piezoelectric vibration energy harvesting systems. IEEE. Trans. Power Electron., 27: 623-627.