ISSN: 1816-949X

© Medwell Journals, 2016

# A Dual Band Concurrent Low Noise Amplifier for Bluetooth and WLAN Applications

<sup>1</sup>Hossein Hadadian, <sup>2</sup>Esmaeil Nagafi Aghdam and <sup>3</sup>Javad Abbaszadeh

<sup>1</sup>Department of Electrical Engineering, Faculty of Engineering,

Shahid Chamran University, Ahvaz, Iran

<sup>2</sup>Microelectronic Research Lab., Sahand University of Technology, Tabriz, Iran

<sup>3</sup>Department of Electronic Engineering, Urmia Branch, Islamic Azad University, Urmia, Iran

Abstract: A fully integrated concurrent dual-band Low Noise Amplifier (LNA) is introduced and simulated in 0.18 µm CMOS technology. The LNA is able to simultaneous operate at two different frequency bands (2.4 and 5.8 GHz) which may use in Bluetooth and WLAN applications. The architecture uses a concurrent cascode LNA with capacitive positive feedback for improving the power gain and provides simultaneous narrow band matching at the both frequencies. The LNA provides very good power gain and matching at both frequencies. Measured results show input return losses of 15.8 and -16.17 dB, output matching of 32.5 and -13.47 dB, power gain is about 19.55 and 15.5 dB and its noise figure is about 1.12 and 1.7 dB at 2.4 and 5.8 GHz, respectively. The circuit delivers 4.09 mA of current from 1.8 V power supply.

Key words: LNA, noise figure, input matching, output matching, CMOS technology

#### INTRODUCTION

With the recent proliferation of wireless transceiver application, there is an extensive effort to develop low cost, highly integrated RF circuit. CMOS has become a competitive technology for radio transceiver implementation due to the technology scaling, higher level of integration ability, lower cost, etc.

The signal delivered by antenna in modern wireless systems can be in the sub-microvolt rang underscores the acute need for low noise amplification.

The low noise amplifier is the most important component to compensate the noise figure in a RF, front-end module. The key design parameters of LNA are the high gain, the low noise figure and high linearity. The linearity becomes more and more important in modern digital wireless system because a complex digital modulation where the RF signals usually have high peak-to-average power ratio. Therefore, a highly linear LNA is demanded in a wireless receiver to reduce inter-modulation distortion. The linearity of LNA is described by its input referred 3rd-order intercept point (Kim et al., 2007).

Furthermore, the transfer characteristics of filter inter posted between the antenna and LNA are frequently quite sensitive to the quality of terminations.

Also, LNA design involves the trade off between these parameters such as Noise Figure (NF), gain, linearity and power consumption. The goal of LNA design is to

achieve simultaneous noise and input matching at any given amount of power dissipation as well as satisfy the linearization conditions. Also, today's requirements of multiband wireless front-end transceivers need multiband low noise amplifiers. One approach is to design multiband LNA using concurrent techniques. This technique describes a circuit works in several bands simultaneously, like that for WiBro, WLAN and bluetooth applications.

## BASIC CONCEPTS OF LNA

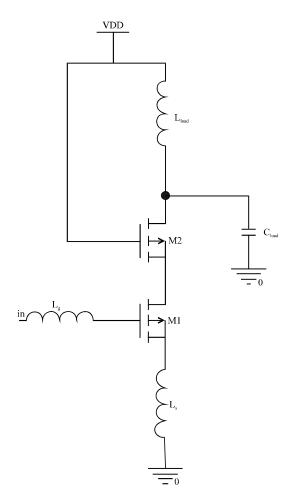

Figure 1 shows a conventional cascode LNA with inductive source degeneration which is widely used as CMOS LNA (Kim *et al.*, 2007).

The input impedance is set by the gate-to-source capacitor so that additional tuning inductor are used to matching it to the source impedance. To provide freedom to both tune the input impedance and minimize the noise figure, one pair of inductor is used. The source degenerated inductor works effectively as a noiseless resistor:

$$R_{L_s} = \omega_T.L_s \tag{1}$$

where,  $\omega_{\scriptscriptstyle T}$  is the cut-off angular frequency and equals:

$$\omega_{\rm T} = \frac{g_{\rm m}}{C_{\rm gs}} \tag{2}$$

The effective transcondutance is given by:

Fig. 1: Conventional LNA

$$g_{meff} = Q_{in} \cdot g_m \tag{3}$$

where,  $Q_{in}$  is the quality factor of the series LC tank at the input which consist of  $L_g$ ,  $L_e$ ,  $C_g$  and  $R_{L_e}$ . The value of  $Q_{in}$  at resonance frequency is given by:

$$Q_{in} = \frac{1}{\omega_{l} C_{\sigma s} \omega_{r} L_{s}}$$

(4)

and when the input impedance is matched to the source impedance  $R_{_{\text{S}}}$  (usually 50  $\Omega)$   $Q_{_{\text{in}}}$  can be expressed by:

$$Q_{in} = \frac{1}{\omega_0 C_{gs} R_s}$$

(5)

and then the effective transconduce is equal with:

$$g_{\text{meff}} = \frac{\omega_{\text{T}}}{\omega_{\text{0}}} \frac{1}{R_{\text{c}}}$$

(6)

When both input and output are impedance matched, the power gain of LNA is given by:

$$A_{p} = \left(\frac{\omega_{r}}{\omega_{0}}\right)^{2} \frac{Q_{L_{0}} \omega_{0} L_{0}}{R_{s}} \tag{7}$$

where,  $L_0$  is the inductance of the output tank circuit. The gate thermal noise, the channel thermal noise and the induced gate noise are major noise contribute in this circuit. The noise factor of this circuit is given by:

$$F = 1 + \frac{R_{L_g}}{R_s} + \frac{R_g}{R_s} + \gamma \chi g_{d0} R_s \left(\frac{\omega_0}{\omega_T}\right)^2$$

(8)

Where

$R_{L_g}$  and  $R_g$  = The parasitic resistance of  $L_g$  and gate parasitic resistance, respectively

χ = The modification factor of the induced gate noise

$\gamma$  = A function of bias

Experimental studies have shown that g may be as high as 2-3 for short channel devices operating in saturation. This value generally increases with increasing drain bias. The increased value of g over the long channel value of 2/3 is evidently due to hot electrons in the channel.

The other most important issue in LNA design is linearity. The linearity of the inductive source degenerated LNA is also dominated by its input transcunductor  $g_m$ . When the input impedance is matched to  $R_s$  the IIP $_3$  is then given by:

$$IIP_{3} = \frac{1}{Q_{in}^{2} R_{s}} \frac{\gamma}{3} \frac{1}{\alpha} V_{od} \left( 1 + \frac{1}{2} \alpha V_{od} \right) (1 + \alpha V_{od})^{2}$$

(9)

where,  $V_{od}$  is the over-drive voltage and  $\alpha$  is given by:

$$\alpha = \theta + \frac{\mu_0}{2V_{cost}L} \tag{10}$$

Where:

$\theta$  = A process constant

$\mu_0$  = The mobility

$V_{od} = Zero$

L = The length of channel

#### CIRCUIT DESCRIPTION

Simultaneous operation at multiple frequency bands in the traditional application of non-concurrent multiband radios may not appear very advantageous. After all for example the mobile phone user will be using any one frequency bond for his/her voice communication at any given time. However, there are numerous cases where

concurrent multiband operation is highly desirable such as front-ends used for multiple application like WLAN and Bluetooth front-ends. Using concurrency one could realizes both of them on a signal front-end.

The key note in the cascode LNA designing is to optimization the size of transistors. As said in Yongqang Ding and Ramesh Harjani. Using matching consideration criteria for optimization transconductance of the circuit the optimal size of transistor might expressed as:

$$\omega_{\text{\tiny opt}} = \frac{1}{3\omega_{\text{\tiny 0}} L_{\text{\tiny eff}} C_{\text{\tiny nx}} R_{\text{\tiny s}}} \tag{11}$$

and then the noise figure of the circuit given by:

$$F = 1 + \frac{2}{3} \frac{\gamma}{\alpha} \frac{\omega_0}{\omega_T} \tag{12}$$

For achieving concurrency characteristics the circuit must uses different matching and tuning networks in the input and output of circuit, respectively.

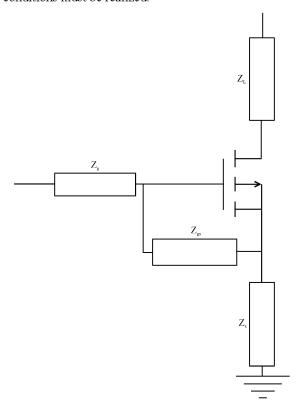

The general model of a typical LNA is shown in Fig. 2 to achieve simultaneous noise and power matching at the input in multiple band of frequency below conditions must be realized.

Fig. 2: General model of a typical LNA for simultaneous noise and power matching at the input

$$Z_{gs}Z_{s}Z_{gs} = 0$$

$$g_{m}Z_{s}Z_{gs} = R_{in} = 50$$

$$\forall \omega_{n} \_band$$

(13)

A simple network that satisfies these conditions is a parallel LC network in series with an inductor. The parallel LC of  $Z_{\rm g}$  resonator with  $Z_{\rm gs}$ + $Z_{\rm s}$  at both frequency bands of interest.

In order to achieve narrow-band gain at bonds of interest, the drain load network should exhibit high impedance only at two frequency bands of interest. This can be done by adding serial LC circuit in parallel with a LC tank.

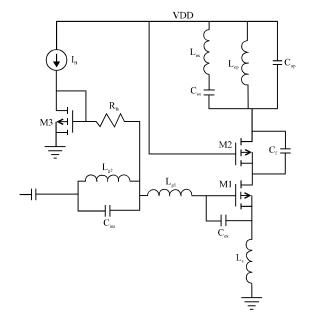

The additional capacitance also adds between gate and source of the amplifier to reduction noise figure in low power dissipation. This capacitance acts as very simple positive feedback that enhances the power gain (Nguyen *et al.*, 2004).

Another capacitor is added between drain and source of the cascode transistor to improve the power gain with another positive feedback. This phenomenon can be understood by another point of view as the form of oscillator (Razavi, 1998, 1999). The effect of the positive feedback will increase maximum available gain of the cascode amplifier at high frequencies.

These additional capacitance dissipated no more DC power and contributed no more noise. This technique is first introduced in Chan. But stability considerations limit the feedback value. The overall circuit schematic is shown in Fig. 3.

Fig. 3: The proposed LNA

Table 1: Comparison of different CMOS LNA design

|       |                 |          | Noise Power dissipation |          |             |       |              |                       |

|-------|-----------------|----------|-------------------------|----------|-------------|-------|--------------|-----------------------|

| Years | Frequency (GHz) | S22 (dB) | S11 (dB)                | S21 (dB) | figure (dB) | (mW)  | Process (µm) | References            |

| 2008  | 2.40            | -32.5    | -15.8                   | 19.5     | 1.12        | 7.36  | 0.18         | This research         |

|       | 5.80            | -13.47   | -16.17                  | 15.5     | 1.70        |       |              |                       |

| 2001  | 2.45            | NA       | -25                     | 14.0     | 2.30        | 10.00 | 0.35         | Hashemi and Hajimiri  |

|       | 5.80            | NA       | -15                     | 15.5     | 4.50        |       |              |                       |

| 2007  | 2.35            | NA       | NA                      | 13.2     | 1.30        | 8.55  | 0.13         | Kim et al. (2007)     |

| 2004  | 0.90            | NA       | -18                     | 12.0     | 1.35        | 2.00  | 0.25         | Nguy en et al. (2004) |

| 2004  | 5.25            | NA       | NA                      | 20.0     | 1.50        | 7.50  | 0.18         | Nguyen                |

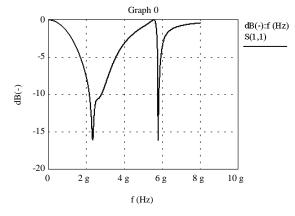

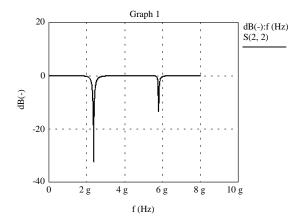

Fig. 4: Input return losses S11

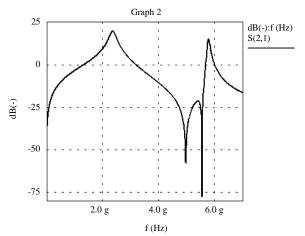

Fig. 5: Output return losses S22

## SIMULATION AND RESULTS

The simulation was done using  $0.18~\mu m$  standard CMOS technology. The designed LNA had on NF of 1.12~dB at Bluetooth receiver band (2.4~GHz) and 1.7~dB at the WLAN band (5.8~GHz).

The input matching parameter S11 shows that the system is matched exactly at desired frequency bands and has a very good input matching characteristic (Fig. 4). The output matching parameter also shows a very good value again exactly at desired bonds (Fig. 5 and 6).

As shown, the power gain of LNA is about 19.55 dB at 2.4 Ghz and 15.5 in 5.8 Ghz. This

Fig. 6: Power gain S21

circuit delivered 4.09 mA from 1.8 V power supply. Compares some of low noise amplifier (Table 1).

## CONCLUSION

A dual band concurrent low noise amplifier for Bluetooth WLAN application is designed and simulation in 0.18  $\mu m$  standard CMOS technology. This structure uses capacitive feedback to improve the power gain. Simulation results show the very low noise figure and good input and output matching characteristics for this circuit both frequency bands of interest. Proposed LNA consumed 7.36 mW of power.

#### REFERENCES

Kim, J., C. Park, H. Kim, B. Kim and Y. Kim, 2007. Improving the linearity of CMOS LNA using the post IM3 compensator. J. Korea Electromagnetic Eng. Soc., Vol. 7.

Nguyen, T.K., C.H. Kim, G.J. Ihm, M.S. Yang and S.G. Lee, 2004. CMOS low-noise amplifier design optimization techniques. IEEE Trans. Microwave Theor. Tech., 52: 1433-1442.

Razavi, B., 1998. RF Microelectronics. Prentice Hall Publisher, New Jersey, USA., Pages: 180.

Razavi, B., 1999. CMOS technology characterization for analog and RF design. IEEE J. Solid State Circuits, 34: 268-276.