ISSN: 1816-949X

© Medwell Journals, 2013

# Design and Optimization of the Power Consumption in 16-bits Shift Register Using Single Edge Triggered D-Flip-Flop

Mohammad Shakeri, Md. Mamun, Labonnah F. Rahman and Fazida Hanim Hashim Department of Electrical, Electronic and Systems Engineering, Universiti Kebangsaan Malaysia, 43600 Bangi, Selangor, Malaysia

Abstract: Designing the low power devices are becoming very important field of research due to the increment of the number of portable devices. In this research, 16-bits shift register circuit design method is proposed using Single Edge Triggered (SET) D-Flip-flop. Moreover, a comparison study between the conventional circuit design and modified design is presented. The proposed circuit is designed using CEDEC 0.18 µm CMOS process. The simulated results show that SET D-FF circuit required lower power than the conventional shift register circuit. However, the conventional circuit required 16-transistors and the proposed design required 10-transistors. Therefore, 10-transistors SET D-flip-flop is the better option for 16-bits shift register.

Key words: Shift register, SET D-FF, portable applications, conventional circuit, transister

### INTRODUCTION

In digital VLSI circuit design, the advanced battery using portable devices like laptops, Personal Digital Assistants (PDA), tablets and cell phones have set more targets. Portable devices become small and smaller with less space for batteries, still the necessity exists on sufficient power supply voltages. Therefore, power dissipation plays an important role in the designing of VLSI circuits (Sahu and Rincon-Mora, 2004).

Shift registers are one of the most commonly used functional devices in digital circuit systems. Most extensive uses of a shift registers are converting serial to parallel interfaces. Shift registers are useful for many circuits which work with the parallel output interfaces to convert the parallel output to serial interfaces (Akter et al., 2008 a, b; Reaz et al., 2003, 2005, 2007 a, b; Marufuzzaman et al., 2010). Moreover, shift registers are required for simple delay circuits. A shift registers consists of many flip-flops attached together. The inputs information are shifted from one position to either left or right depending on the kind of design of the circuit (Nagapavani et al., 2011). One of the most power consuming and complex circuits in the structures of shift registers blocks are flip-flops. Flip-flops consume about 30-70% of the total power of the system (Stojanovic and Oklobdzija, 1999).

Two kinds of flip-flops in shift registers Single Edge Triggered (SET) and Double Edge Triggered (DET) are widely used. The simplest flip-flops circuits are single edge-triggered which can sample data either on rising or falling clock edge only. The SET flip-flop is commonly performs as the master-slave interface. Single edge triggered D-flip-flops circuits were made to reduce the power delay or area (Reaz et al., 2006; Reaz and Wei, 2004; Mohd-Yasin et al., 2004; Mogaki et al., 2007; Rasouli et al., 2005). To reduce the area, power and delay several research have been made with a balance among these 3 areas (Hossain et al., 1994).

Other type of flip-flops which can be use in the shift registers are double edge triggered. In double edge triggered methods, data can be sampled on each clock edges. Moreover, SET D-flip-flops (SET D-FF) have less energy consumption than SET flip-flops. On the other hand, double-edge triggered flip-flops have bad performance when compared with single-edge circuits because of more complex circuits. In addition, most of the complexities create affect on the signal through the way (Nedovic *et al.*, 2002). Flip-flops which are used in the shift registers can be static or dynamic. Dynamic flip-flop creates fault logic levels when the clocks are removed due to the fact of charge leakage from the output node capacitances. Conversely, static FF holds the output state even though the clock is removed.

In this study, 16-bits SIPO shift register with 10-transistor SET DFF design is presented with reduced area and power dissipation. The designed shift register circuit is suitable for the design of low power applications.

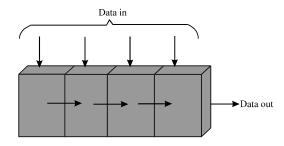

Fig. 1: Parallel in serial out block diagram

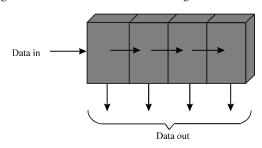

Fig. 2: Serial in parallel out block diagram

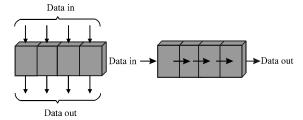

Fig. 3: Parallel in parallel out/serial in serial out block diagram

Architecture of shift register: There are different types of shift registers exists, such as Serial Input and Serial Output (SISO), Serial Input and Parallel Output (SIPO), Parallel Input and Serial Output (PISO) and Parallel Input and Parallel Output (PIPO). Parallel input serial output shift registers are commonly used to add more inputs to a microprocessor to the other devices. In PISO, each pin is interfaced to a parallel input of the shift register and the data will sent via serial to the microprocessor using several fewer inputs than originally needed (Fujiwara et al., 2003; He et al., 2010). Figure 1 shows the block diagram of the PISO shift register.

SIPO shift registers can be used to interface the output of microprocessors to the other devices when the output pins are required more than the available pins. The mechanism of SIPO helps to control many devices using only three or four pins. Figure 2 shows the block diagram of the SIPO shift register.

The other types of shifters are commonly used as a buffer on the circuits such as compact disc drives

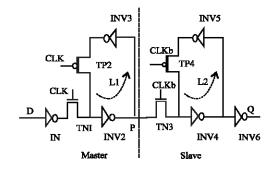

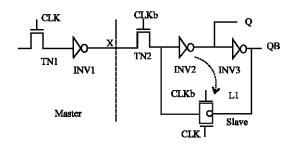

Fig. 4: Conventional 16-transistors using in the shift registers (Nogawa and Ohtomo, 1998)

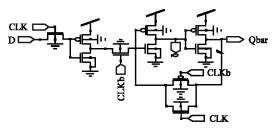

Fig. 5: Schematice diagram of the 10-T SET DFF shift register (Rasouli *et al.*, 2005)

or floppy disc drives. Figure 3 shows the block diagram of the SISO and PIPO shift register. Generally, SET D-FFs are using in the structure of shift registers. Conventional 16-transistors SET D-FFs are working at both rising edge and falling edge of the clock. For the functionality of the SET D-FF, the input must be stay constant just right before setup time (t-setup) and just right after hold time (t-hold), the triggers edges of the clock. The circuit as shown in Fig. 4 shows a conventional type of 16-transistors SET D-FF. From Fig. 4, it is clear that conventional shift register operates in a master and slave parts which are determined by dashed vertical line. A PMOS transistor is used as the feedback path. In the noisy areas, pass transistors can be replaced by transmission gates.

Figure 5 shows the circuit diagram of 10-transistor (10-T) fall edge triggered SET DFF (Sharma et al., 2009). In this circuit, the feedback of the master part is deleted and transmission gate is included in slave feedback part. When clock is 1 master loop is in operation and the inverted data is stored in the point X. When the clock level is going to 0 the slave loop including transistor TN2 and feedback loop L1 is going to operational and generates data at the output Q and QB. When the clock is removed or grounded, the SET DFF stay in the previous level which is the main advantage of the SET D-FF. In addition, the SET D-FF is static naturally which is useful for the shift register (Sharma et al., 2010a).

### MATERIALS AND METHODS

For the design method of 16 bits shift register, first 1-bit cell is designed to make one SET DFF. The

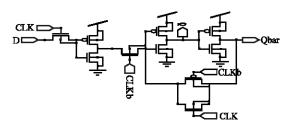

Fig. 6: Schematic diagram of the STGB bias 10-transistor (Sharma *et al.*, 2010b)

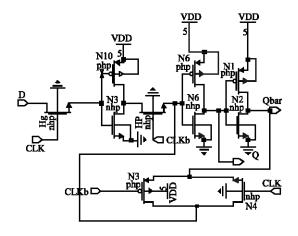

Fig. 7: NBB bias 10-transistor schematic (Sharma *et al.*, 2011)

Fig. 8: Schematic diagram of 1-bit of the 16-bits shift register

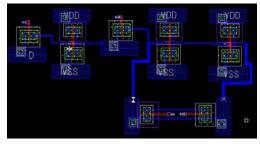

Fig. 9: The layout of one bit of 16-bits shift register

similar process has been followed to expand the design for 16-bits. In this case, two types of SET 10-transistor DFF are designed. Firstly, Sub Threshold Grounded Body (STGB) bias 10-transistor is required (Sharma *et al.*, 2010a). In this kind of circuits, the body of the transistors is connected to the GND as shown in Fig. 6 with the STGB bias 10-transistor circuit.

Secondly, No Body Bias (NBB) 10-transistor SET D-FF is the required structures for the design method. In this type of circuit, the substrate of the transistors are connected to the source and thus of the transistors are always zero. Therefore, the structure is known as No Body Bias (NBB) condition (Stojanovic and Oklobdzija, 1999). Figure 7 shows the NBB 10-transistors circuit schematic diagram.

The schematic of the 1-bit DFF used in this research designed by CEDEC 0.18  $\mu m$  CMOS process is shown in Fig. 8.

The modified low voltage-type 16-bits shift register layout is also designed in CEDEC 0.18  $\mu$ m CMOS process as shown in Fig. 9. The 1-bit layout of the 16-bits shift register is shown in Fig. 9. For the sizing of the transistor, W/L = 0.18/0.18  $\mu$ m is utilized for each CMOS transistors.

### RESULTS AND DISCUSSION

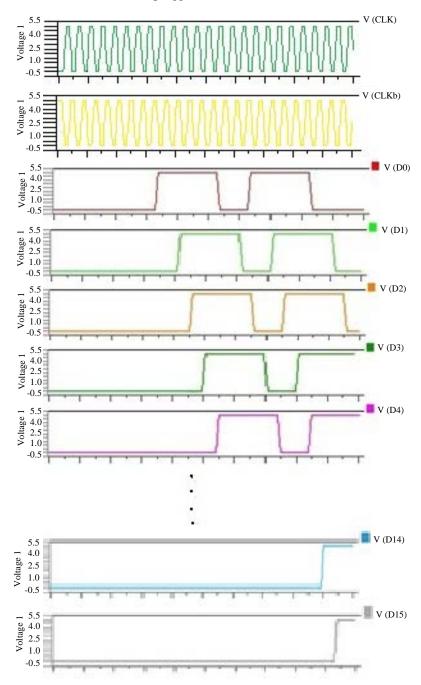

CEDEC 0.18  $\mu m$  CMOS process is used to measure the output results of the proposed 16-bits SET DFF shift register circuit with the ELDONET simulator. The 1.8 V power supply voltage and 27°C operating condition is used for the 16-bits SET-DFF shift register circuit design.

A comparison study of the power consumption among 16-bits shift register with 16-transistor and 10-transistor SET DFF design is shown in Table 1. It can be clearly seen from Table 1 that the power consumption of the 10-transistor circuit is less than the conventional one. Therefore, 10-transistors SET DFF design is noted in this research.

Moreover, a comparison study between the STGB and the NBB type shift register is presented in Table 2. It is obvious that the NBB shift register dissipates less power than the STGB. In addition, NBB shift register consumes lowest power among all the previous designs. Therefore, it is a better choice to design the circuit for the shift register.

Table 1: Comparison study between the proposed and conventional design

16-bits shift register using SET DFF

Power consumption

Conventional flip-flops

$83.68 e^{-5}$

10-transistors technology

$82.08 e^{-6}$

Table 2: Comparison of power consumption between STGB and NBB

Research

Power consumption (watt)

NBB (Sharma et al., 2011)

7.287432e-009

STGB

1.179902e-008

Fig. 10: The result of 16-bits shift registers using 10-transistors DFF

The simulated result of the 16-bits shift register is shown in Fig. 10. The performance of 16-bits shift register using 10-transistors DFF produce satisfactory outputs which is clearly shown in Fig. 10.

## CONCLUSION

In this study, the design method of 16-bits shift register using the proposed 10-transistor SET DFF is described. In VLSI design, power consumption and area are the two major things for applicable devices. Moreover, comparison study shows that the NBB scheme for shift register circuit produced better performance in terms of power dissipation among the other designed circuits. The simulation outputs are found satisfactory using CEDEC 0.18  $\mu$ m CMOS process. Therefore, among all the shift register design methods, NBB

design of negative edge triggered SET DFF circuit is suitable for power efficient portable devices.

#### REFERENCES

- Akter, M., M.B.I. Reaz, F. Mohd-Yasin and F. Choong, 2008a. A modified-set partitioning in hierarchical trees algorithm for real-time image compression. J. Commun. Technol. Elect., 53: 642-650.

- Akter, M., M.B.I. Reaz, F. Mohd-Yasin and F. Choong, 2008b. Hardware implementations of an image compressor for mobile communications. J. Commun. Technol. Elect., 53: 899-910.

- Fujiwara, K., H. Hoshina, Y. Yamashiro and N. Yoshikawa, 2003. Design and component test of SFQ shift register memories. IEEE Trans. Applied Superconductivity, 13: 555-558.

- He, C., C. Liao, Y. Liang and S. Zhang, 2010. A new integrated gate driver with shift register circuits employing 4 clocks for 14.1-inch TFT-LCD. Proceedings of the International Conference on Electrical and Control Engineering, June 25-27, 2010, Wuhan, China, pp. 149-152.

- Hossain, R., L.D. Wronski and A. Albicki, 1994. Low power design using double edge triggered flip-flops. IEEE Trans. Very Large Scale Integration Syst., 2: 261-265.

- Marufuzzaman, M., M.B.I. Reaz, M.S. Rahman and M.A.M. Ali, 2010. Hardware prototyping of an intelligent current dq PI controller for FOC PMSM drive. Proceedings of 6th International Conference on Electrical and Computer Engineering, December 18-20, 2010, IEEE, Dhaka, Bangladesh, pp: 86-88.

- Mogaki, S., M. Kamada, T. Yonekura, S. Okamoto, Y. Ohtaki and M.B.I. Reaz, 2007. Time-stamp service makes real-time gaming cheat-free. Proceedings of the 6th Annual Workshop on Network and Systems Support for Games: Netgames 2007, September 19-20, Melbourne, Australia, pp. 135-138.

- Mohd-Yasin, F., A.L. Tan and M.I. Reaz, 2004. The FPGA prototyping of iris recognition for biometric identification employing neural network. Proceedings of the 16th International Conference on Microelectronics, December 6-8, 2004, Tunis, Tunesia, pp. 458-461.

- Nagapavani, T., V. Rajmohan and P. Rajendaran, 2011.

Optimized shift register design using reversible logic.

Proceedings of the 3rd International Conference on Electronics Computer Technology, April 8-10, 2011, Chennai, India, pp. 236-239.

- Nedovic, N., M. Aleksic and V.G. Oklobdzija, 2002. Comparative analysis of double-edge versus single-edge triggered clocked storage elements. Proceedings of the IEEE International Symposium on Circuits and Systems, May 26-29, 2002, Scottsdale, Arizona, pp. V-105-V-108.

- Nogawa, M. and Y. Ohtomo, 1998. A data-transition look-ahead DFF circuit for statistical reduction in power consumption. IEEE J. Solid-State Circuits, 33: 702-706.

- Rasouli, S.H., V. Khademzadeh, A. Afzali-Kusha and M. Nourani, 2005. Low-power single- and double-edge-triggered flip-flops for high-speed applications. IEE Proc. Circuits Devices Syst., 152: 118-122.

- Reaz, M.B.I., M.T. Islam, M.S. Sulaiman, M.A.M. Ali, H. Sarwar and S. Rafique, 2003. FPGA realization of multipurpose FIR filter. Proceedings of the Parallel and Distributed Computing, Applications and Technologies, August 27-29, 2003, Chengdu, pp: 912-915.

- Reaz, M.B.I. and L.S. Wei, 2004. Adaptive linear neural network filter for fetal ECG extraction. Proceedings of the International Conference on Intelligent Sensing and Information Processing, January 4-7, 2004, Chennai, India, pp. 321-324.

- Reaz, M.B.I., F. Mohd-Yasin, S.L. Tan, H.Y. Tan and M.I. Ibrahimy, 2005. Partial encryption of compressed images employing FPGA. Proceedings of the IEEE International Symposium on Circuits and Systems, May 23-26, 2005, Kobe, Japan, pp. 2385-2388.

- Reaz, M.B.I., F. Choong and F. Mohd-Yasin, 2006. VHDL modeling for classification of power quality disturbance employing wavelet transform, artificial neural network and fuzzy logic. Simulation, 82: 867-888.

- Reaz, M.B.I., F. Choong, M.S. Sulaiman and F. Mohd-Yasin, 2007a. Prototyping of wavelet transform, artificial neural network and fuzzy logic for power quality disturbance classifier. Elect. Power Compon Syst., 35: 1-17.

- Reaz, M.B.I., M.I. Ibrahimy, F. Mohd-Yasin, C.S. Wei and M. Kamada, 2007b. Single core hardware module to implement encryption in TECB mode. Informacije MIDEM J. Microelect. Elect. Compon. Mater., 37: 165-171.

- Sahu, B. and A.G. Rincon-Mora, 2004. A low voltage, dynamic, noninverting, synchronous buck-boost converterfor portable applications. IEEE Trans Power Electron., 19: 443-452.

- Sharma, M., A. Noor, S.C. Tiwari and K. Singh, 2009. An area and power efficient design of single edge triggered D-flip flop. Proceedings of the International Conference on Advances in Recent Technologies in Communication and Computing, October 27-28, 2009, Noida, India, pp:478-481.

- Sharma, M., K.G. Sharma, T. Sharma, B.P. Singh and N. Arora, 2010a. SET D-flip flop design for portable applications. Proceedings of the International Conference on Power Electronics (IICPE), January 28-30, 2010, Lakshmangarh, India, pp: 1-5.

- Sharma, T., K. Sharma, B. Singh and N. Arora, 2010b. Efficient interconnect design with novel repeater insertion for low power applications. WSEAS Transa. Circuits Syst., 9: 153-162.

- Sharma, K.G., T. Sharma, B.P. Singh and M. Sharma, 2011. Modified SET D-Flip flop design for low-power VLSI applications. Proceedings of the International Conference on Devices and Communications (ICDeCom), February 24-25, 2011, Mesra, India, pp:1-5.

- Stojanovic, V. and V.G. Oklobdzija, 1999. Comparative analysis of master-slave latches and flip-flops for high-performance and low-power systems. IEEE J. Solid-State Circuits, 34: 536-548.